# NTE74S194 Integrated Circuit TTL – 4–Bit Bidirectional Universal Shift Register

### **Description:**

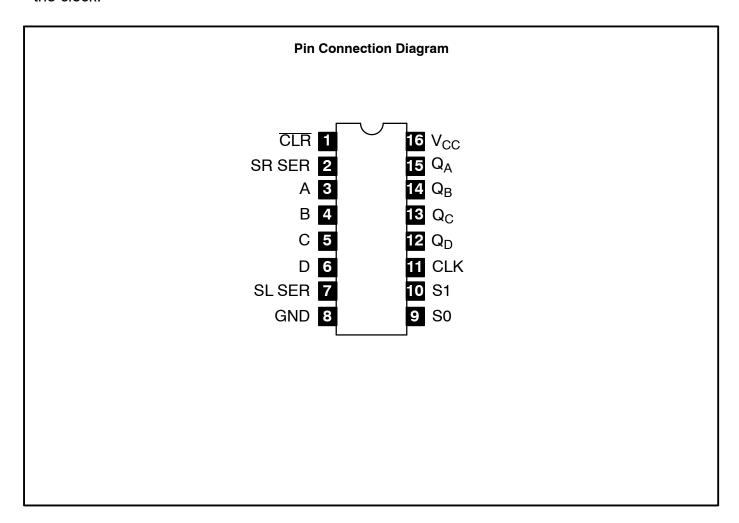

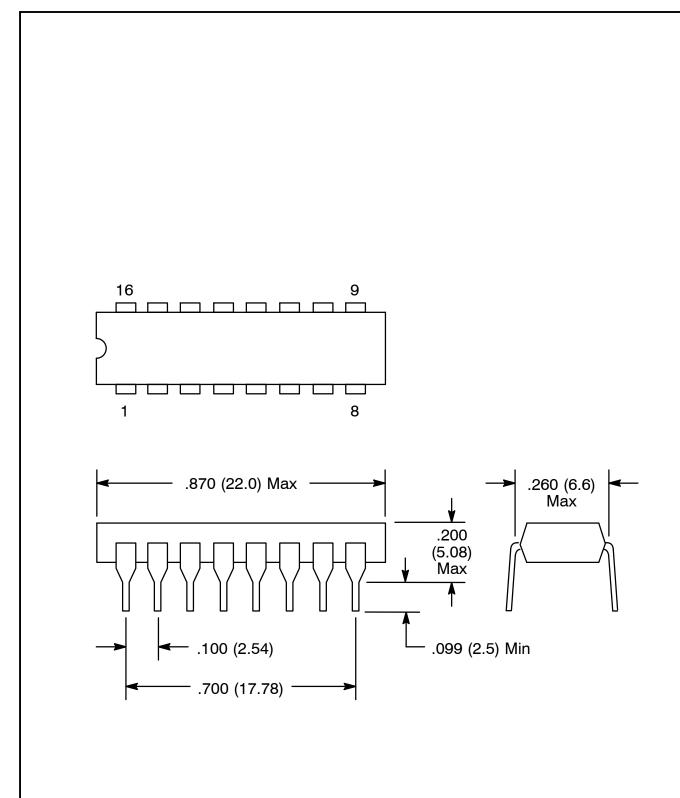

The NTE74S194 is a 4-bit bidirectional shift register in a 16-Lead plastic DIP type package designed to incorporate virtually all of the features a system designer may want is a shift register. The circuit contains 46 equivalent gates and features parallel inputs, parallel outputs, right-shift and left-shift serial inputs, operating-mode-control inputs, and a direct overriding clear line. The register has four distinct modes of operation, namely:

Inhibit Clock (Do Nothing) Shift Right (In the Direction  $Q_A$  Toward  $Q_D$ ) Shift Left (In the Direction  $Q_D$  Toward  $Q_A$ ) Parallel (Broadside) Load

Synchronous parallel loading is accomplished by applying the four bits of data and taking both mode control inputs, S0 and S1, high. The data are loaded into the associated flip-flops and appear at the outputs after the positive transition of the clock input. During loading, serial data flow is inhibited.

Shift right is accomplished synchronously with the rising edge of the clock pulse when S0 is high and S1 is low. Serial data for this mode is entered at the shift-right data input. When S0 is low and S1 is high, data shifts left synchronously and new data is entered at the shift-left serial input.

Clocking of the shift register is inhibited when both control inputs are low.

#### Features:

- Parallel Inputs and Outputs

- Four Operating Modes:

Synchronous Parallel Load

Right Shift

Left Shift

Do Nothing

- Positive Edge-Triggered Clock

- Direct Overriding Clear

# Absolute Maximum Ratings: (Note 1)

| Supply Voltage, V <sub>CC</sub>             | 7V                   |

|---------------------------------------------|----------------------|

| DC Input Voltage, V <sub>IN</sub>           | 5.5V                 |

| Power Dissipation, P <sub>D</sub>           | 425mW                |

| Operating Temperature Range, T <sub>A</sub> | $\dots$ 0°C to +70°C |

| Storage Temperature Range, T <sub>stq</sub> | -65°C to +150°C      |

Note 1. Unless otherwise specified, all voltages are referenced to GND.

## **Recommended Operating Conditions:**

| Parameter                           | Symbol                | Min  | Тур | Max  | Unit |

|-------------------------------------|-----------------------|------|-----|------|------|

| Supply Voltage                      | V <sub>CC</sub>       | 4.75 | 5.0 | 5.25 | V    |

| High-Level Output Current           | I <sub>OH</sub>       | _    | _   | -1   | mA   |

| Low-Level Output Current            | l <sub>OL</sub>       | _    | _   | 20   | mA   |

| Clock Frequency                     | f <sub>clock</sub>    | 0    | _   | 70   | MHz  |

| Width of Clock Pulse                | t <sub>w(clock)</sub> | 7    | _   | _    | ns   |

| Width of Clear Pulse                | t <sub>w(clear)</sub> | 12   | _   | _    | ns   |

| Mode Control Setup Time             | t <sub>su</sub>       | 11   | _   | _    | ns   |

| Serial and Parallel Data Setup Time | t <sub>su</sub>       | 5    | _   | _    | ns   |

| Clear Inactive-State Setup Time     | t <sub>su</sub>       | 9    | _   | _    | ns   |

| Hold Time at Any Input              | t <sub>h</sub>        | 3    | _   | _    | ns   |

| Operating Temperature Range         | T <sub>A</sub>        | 0    | -   | +70  | °C   |

### **Electrical Characteristics**: (Note 2, Note 3)

| Parameter                    | Symbol          | Test Conditions                                                 | Min | Тур | Max  | Unit |

|------------------------------|-----------------|-----------------------------------------------------------------|-----|-----|------|------|

| High-Level Input Voltage     | V <sub>IH</sub> |                                                                 | 2   | _   | _    | V    |

| Low-Level Input Voltage      | $V_{IL}$        |                                                                 | _   | _   | 0.8  | V    |

| Input Clamp Voltage          | V <sub>IK</sub> | V <sub>CC</sub> = MIN, I <sub>I</sub> = -18mA                   | -   | _   | -1.2 | V    |

| High Level Output Voltage    | V <sub>OH</sub> | $V_{CC} = MIN, V_{IH} = 2V, V_{IL} = 0.8V, I_{OH} = -1mA$       | 2.7 | 3.4 | _    | V    |

| Low Level Output Voltage     | V <sub>OL</sub> | $V_{CC}$ = MIN, $V_{IH}$ = 2V, $V_{IL}$ = 0.8V, $I_{OL}$ = 20mA | -   | _   | 0.5  | V    |

| Input Current                | I <sub>I</sub>  | $V_{CC} = MAX, V_I = 5.5V$                                      | -   | _   | 1    | mA   |

| High Level Input Current     | I <sub>IH</sub> | $V_{CC} = MAX, V_I = 2.7V$                                      | -   | _   | 50   | μΑ   |

| Low Level Input Current      | I₁∟             | $V_{CC} = MAX, V_I = 0.5V$                                      | -   | _   | -2   | mA   |

| Short-Circuit Output Current | los             | V <sub>CC</sub> = MAX, Note 4                                   | -40 | _   | -100 | mA   |

| Supply Current               | I <sub>CC</sub> | V <sub>CC</sub> = MAX, Note 5                                   | -   | 85  | 135  | mA   |

- Note 2. .For conditions shown as MIN or MAX, use the appropriate value specified under "Recommended Operation Conditions".

- Note 3. All typical values are at  $V_{CC} = 5V$ ,  $T_A = +25$ °C.

- Note 4. Not more than one output should be shorted at a time and duration of short-circuit should not exceed one second.

- Note 5. With all outputs open, inputs A through D grounded, and 4.5V applied to S0, S1, clear, and the serial inputs, I<sub>CC</sub> is measured with momentary GND, then 4.5V applied to clock.

# <u>Switching Characteristics</u>: $(V_{CC} = 5V, T_A = +25^{\circ}C \text{ unless otherwise specified})$

| Parameter                           | Symbol           | Test Conditions               | Min | Тур  | Max  | Unit |

|-------------------------------------|------------------|-------------------------------|-----|------|------|------|

| Maximum Clock Frequency             | f <sub>max</sub> | $R_L = 280\Omega, C_L = 15pF$ | 70  | 105  | _    | MHz  |

| Propagation Delay Time (from Clear) | t <sub>PHL</sub> |                               | _   | 12.5 | 18.5 | ns   |

| Propagation Delay Time (from Clock) | t <sub>PLH</sub> |                               | 4   | 8    | 12   | ns   |

|                                     | t <sub>PHL</sub> |                               | 4   | 11   | 16.5 | ns   |

### **Function Table:**

| Inputs |    |    |       |      |       |          |   | Outputs |   |                 |                 |                |                 |

|--------|----|----|-------|------|-------|----------|---|---------|---|-----------------|-----------------|----------------|-----------------|

|        | Мо | de |       | Se   | rial  | Parallel |   |         |   |                 |                 |                |                 |

| Clear  | S1 | S0 | Clock | Left | Right | Α        | В | С       | D | $Q_A$           | $Q_B$           | Q <sub>C</sub> | $Q_D$           |

| L      | Χ  | Χ  | Х     | Χ    | Х     | Χ        | Х | Х       | Χ | L               | L               | L              | L               |

| Н      | Χ  | Χ  | L     | Χ    | Х     | Χ        | Χ | Х       | Χ | Q <sub>A0</sub> | Q <sub>B0</sub> | $Q_{C0}$       | $Q_{D0}$        |

| Н      | Н  | Н  | 1     | Χ    | Х     | а        | b | С       | d | а               | b               | С              | d               |

| Н      | L  | Н  | 1     | Χ    | Н     | Χ        | Χ | Х       | Χ | Н               | $Q_{An}$        | $Q_{Bn}$       | $Q_{Cn}$        |

| Н      | L  | Н  | 1     | Χ    | L     | Χ        | Χ | Х       | Χ | L               | $Q_{An}$        | $Q_{Bn}$       | Q <sub>Cn</sub> |

| Н      | Н  | L  | 1     | Н    | Х     | Χ        | Х | Х       | Х | $Q_{Bn}$        | $Q_{Cn}$        | $Q_{Dn}$       | Н               |

| Н      | Н  | Ĺ  | 1     | L    | Х     | Χ        | Х | Х       | Х | $Q_{Bn}$        | Q <sub>Cn</sub> | $Q_{Dn}$       | L               |

| Н      | L  | L  | Х     | Χ    | Х     | Χ        | Χ | Х       | Χ | Q <sub>A0</sub> | Q <sub>B0</sub> | $Q_{C0}$       | $Q_{D0}$        |

H = HIGH Level (Steady State)

L = LOW Level (Steady State)

X = Irrelevant (Any input, including transitional)

↑ = Transition from LOW to HIGH Level

a, b, c, d = The level of steady-state input at inputs A, B, C, or D respectively

$Q_{A0}$ ,  $Q_{B0}$ ,  $Q_{C0}$ ,  $Q_{D0}$  = The level of  $Q_A$ ,  $Q_B$ ,  $Q_C$ , or  $Q_D$  respectively, before the indicated steady-state input conditions were established

$Q_{An}$ ,  $Q_{Bn}$ ,  $Q_{Cn}$ ,  $Q_{Dn}$  = The level of  $Q_A$ ,  $Q_B$ ,  $Q_C$  respectively, before the most recent  $\uparrow$  transition of the clock.